Post History

This question popped up in the feed and I got curious. Here is what I could find. Note that I am not an IC engineer so my interpretation of some facts may be off. The 3.3V level is defined in the ...

#1: Initial revision

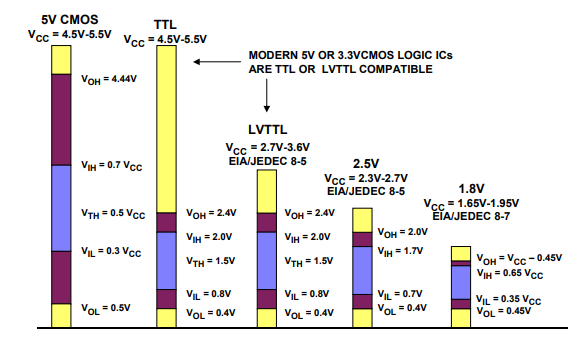

This question popped up in the feed and I got curious. Here is what I could find. Note that I am not an IC engineer so my interpretation of some facts may be off. The 3.3V level is defined in the JESD8 standard. It was made by [JEDEC](https://en.wikipedia.org/wiki/JEDEC). 3.3V is a stepping stone on the path of decreasing supply voltages. This came about because of the improvements in chip design and introduction of CMOS, which in turn moved the optimal operating voltage down. This standard is nice in that it also provides some backward compatibility: if you look at it, its logic levels are compatible with TTL, so this means CMOS chips can work with TTL chips. See the chart below for the logic level comparison ([Analog Devices](https://www.analog.com/media/en/training-seminars/tutorials/MT-098.pdf)). Note that the standard actually allows operation at the 3V level and calls it the "Extended range". Why the number 3.3? This seems to go way back in the 90's to the development of the first ICs. I can find some anecdotal evidence about this level being a consequence of RTL design in the early days of semiconductor technology, but nothing that I can reference. So in short: we use 3.3V now because it is a standard. The value itself comes from the properties of silicon and semiconductors that the early manufacturers used. Why that is is a question for the history buffs on this site.