Post History

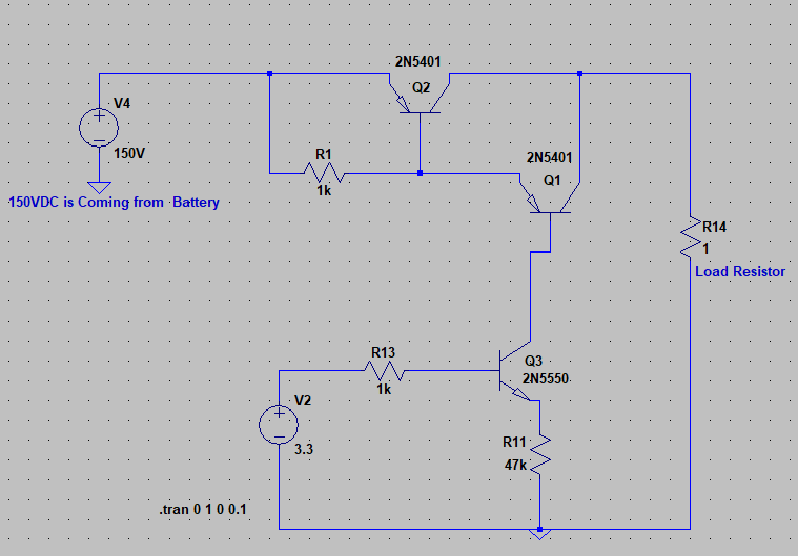

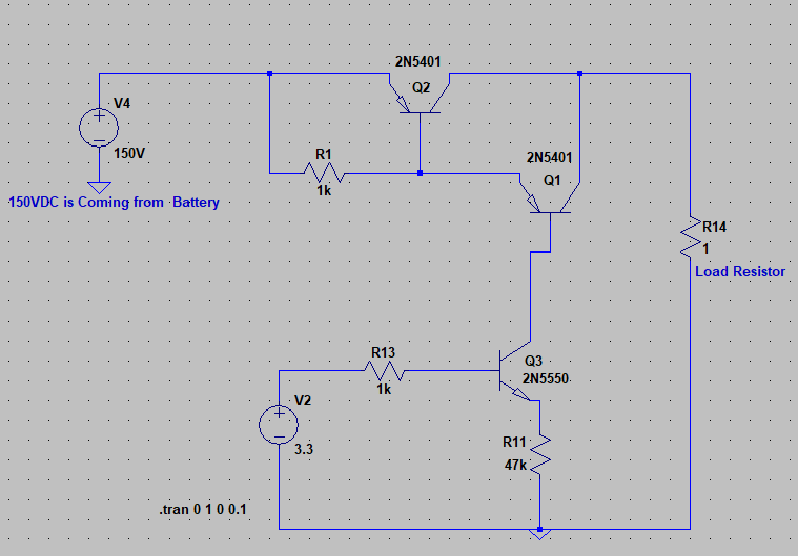

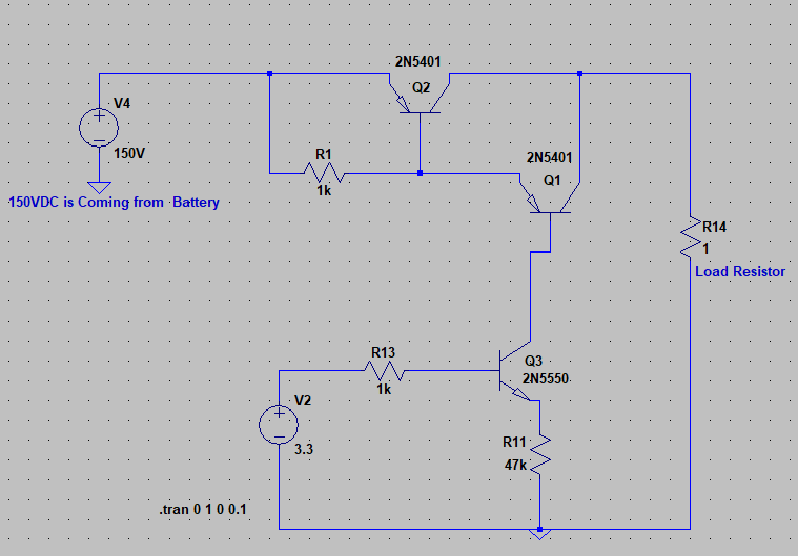

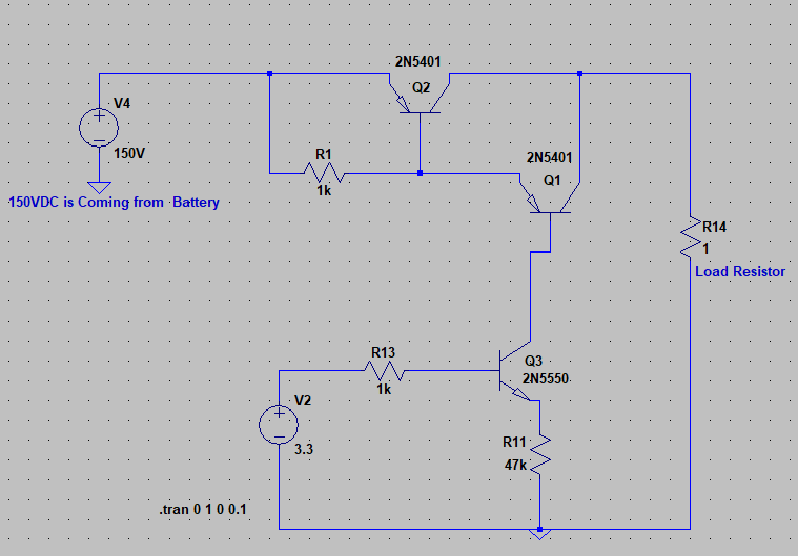

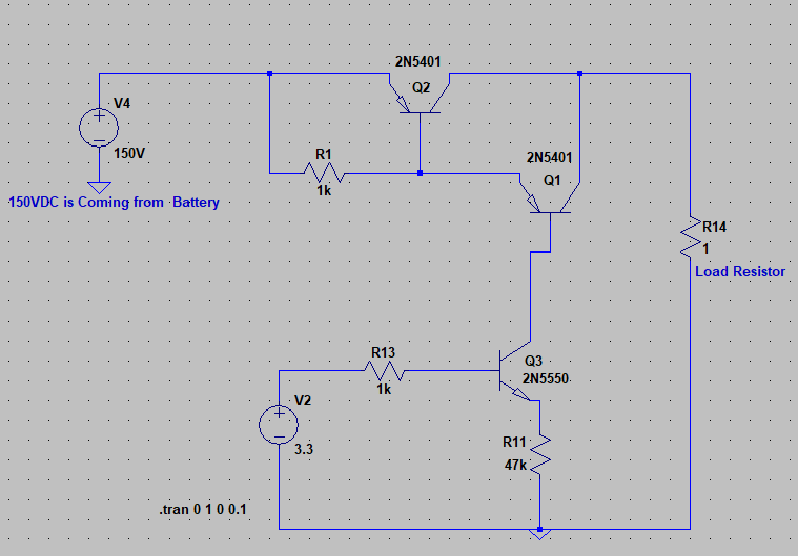

I am trying to analyse what is controlling the load current in the below Darlington configuration. Is it the base current of transistor Q3 which is controlling current through R14 / emitter curr...

#5: Post edited

- I am trying to analyse what is controlling the load current in the below Darlington configuration.

- 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2?

-

- 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?

- 3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.

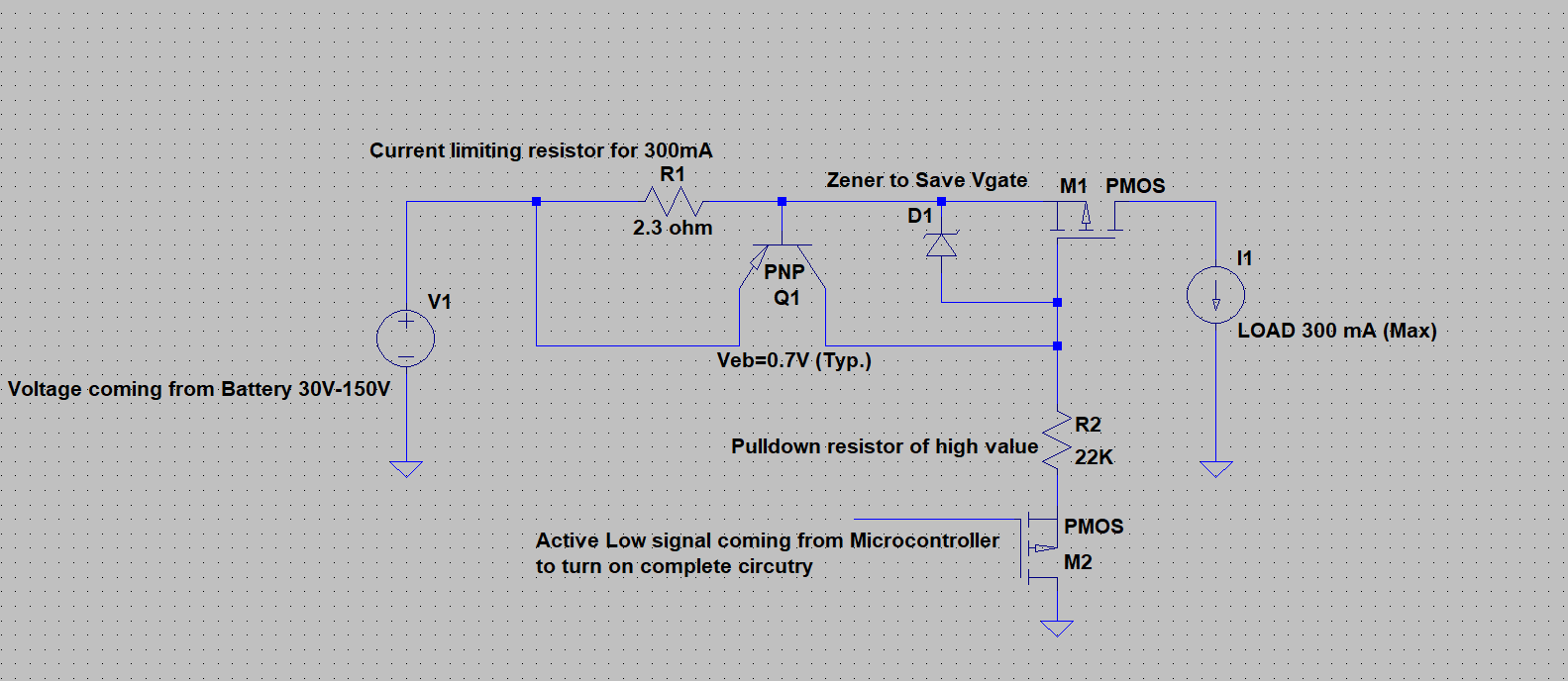

- EDIT :

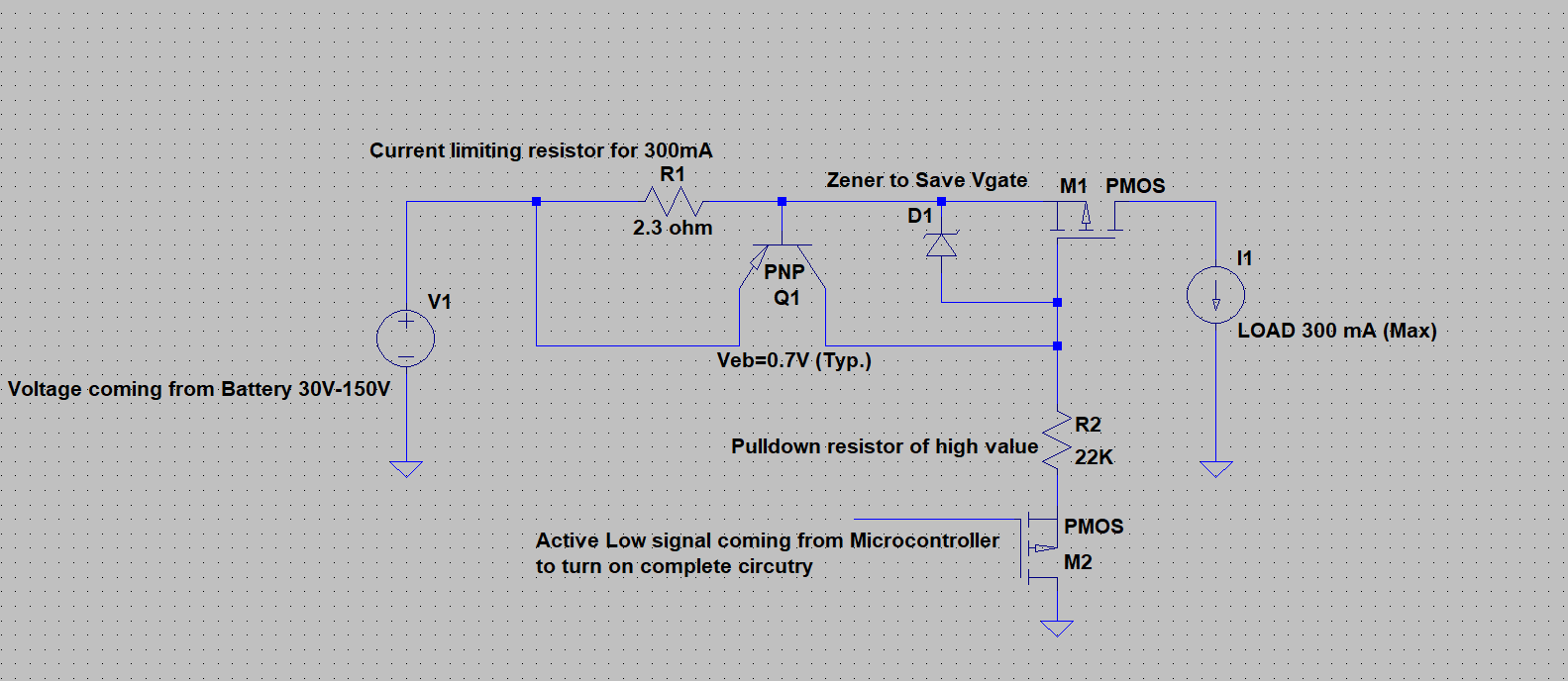

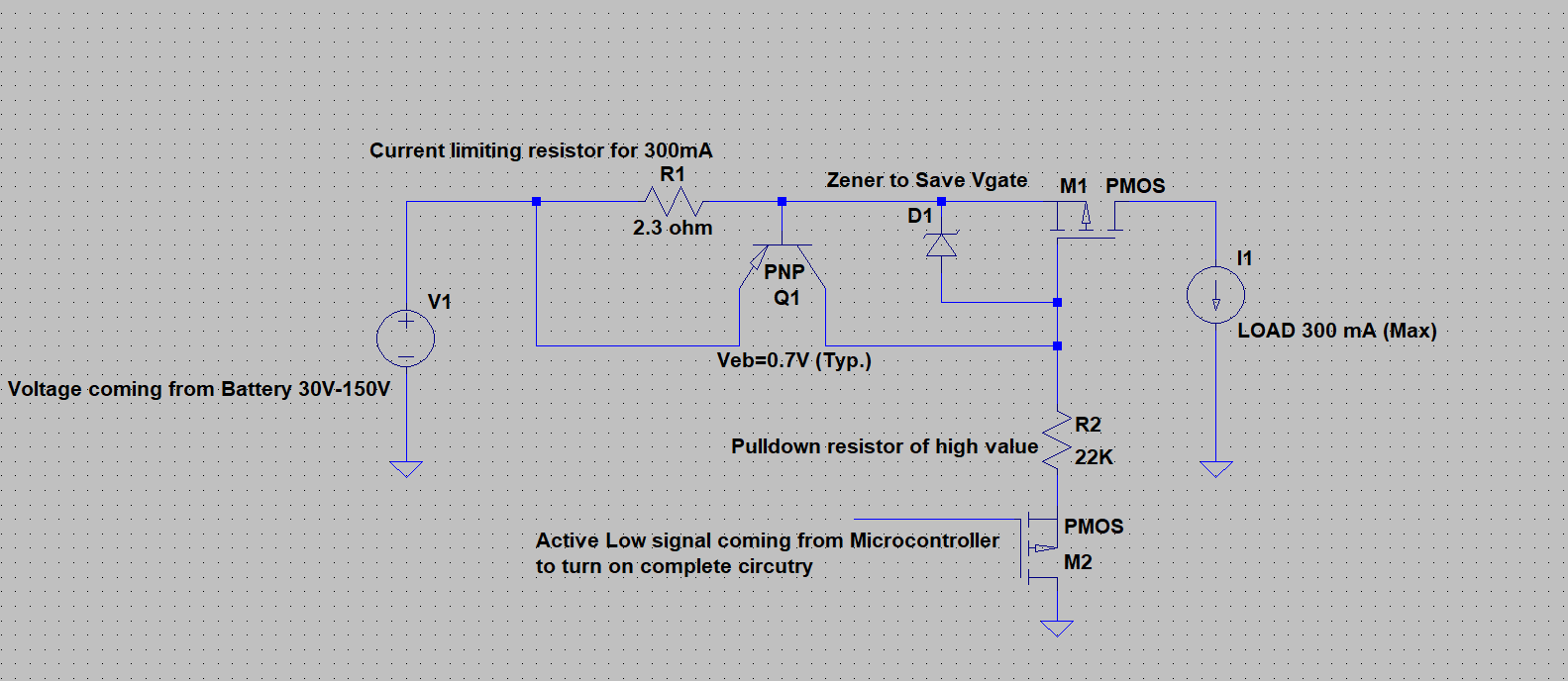

Alternate circuit to acheive the same functionality-

- are there any drawbacks to use this circuit ?

- I am trying to analyse what is controlling the load current in the below Darlington configuration.

- 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2?

-

- 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?

- 3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.

- EDIT :

- Alternate circuit to achieve the same functionality

-

- are there any drawbacks to use this circuit ?

#4: Post edited

- I am trying to analyse what is controlling the load current in the below Darlington configuration.

- 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2?

-

- 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?

3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.

- I am trying to analyse what is controlling the load current in the below Darlington configuration.

- 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2?

-

- 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?

- 3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.

- EDIT :

- Alternate circuit to acheive the same functionality

-

- are there any drawbacks to use this circuit ?

#3: Post edited

- I am trying to analyse what is controlling the load current in the below Darlington configuration.

- 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2?

- 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?

- 3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.

- I am trying to analyse what is controlling the load current in the below Darlington configuration.

- 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2?

-

- 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?

- 3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.

#2: Post edited

**PNP Darlington pair as a current limiter**

- PNP Darlington pair as a current limiter

#1: Initial revision

**PNP Darlington pair as a current limiter**

I am trying to analyse what is controlling the load current in the below Darlington configuration. 1. Is it the base current of transistor Q3 which is controlling current through R14 / emitter current of Q2? 2. If it is, then is the maximum permissible load current is calculated by Ic(Q3) * Q1 beta * Q2 beta ?  3. From light load to maximum load, will all three transistor stay in the active region? For light loads , Q2 may get into saturation region I suppose.