Post History

In protocol I2S we have 3 signal + one none standard master clock(Mentioined by Olin Lathrop): 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock) Question 1: Why we...

#5: Post edited

- In protocol I2S we have 3 signal + one none standard master clock(Mentioined by Olin Lathrop):

- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

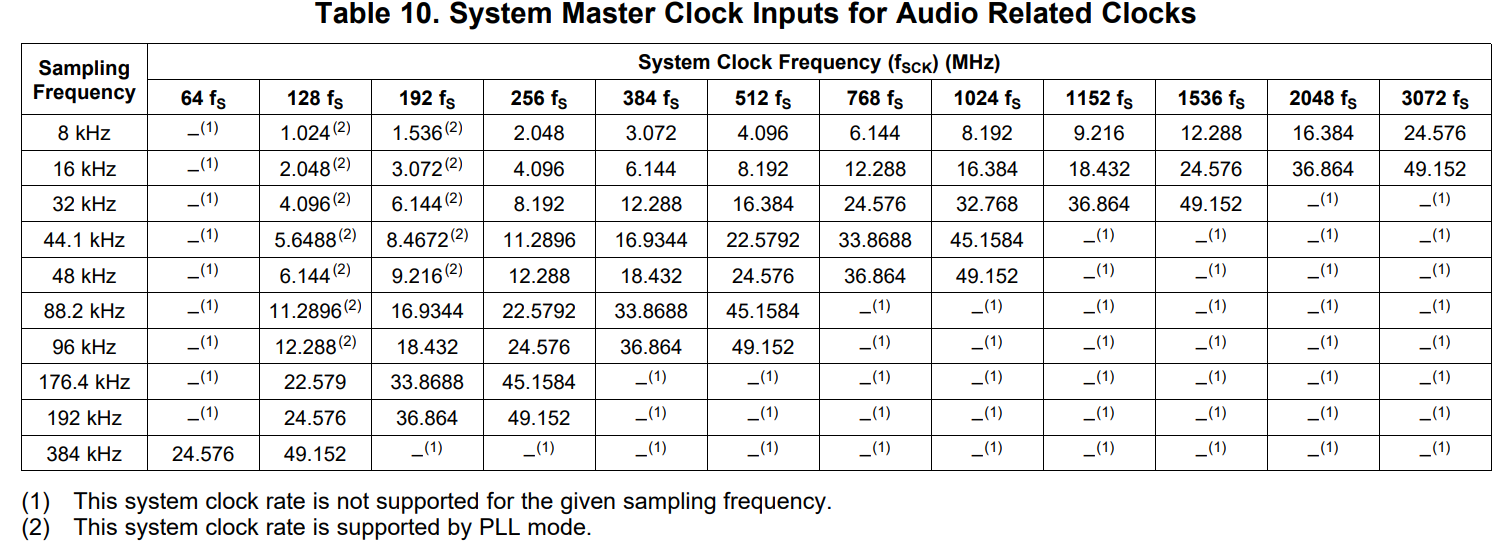

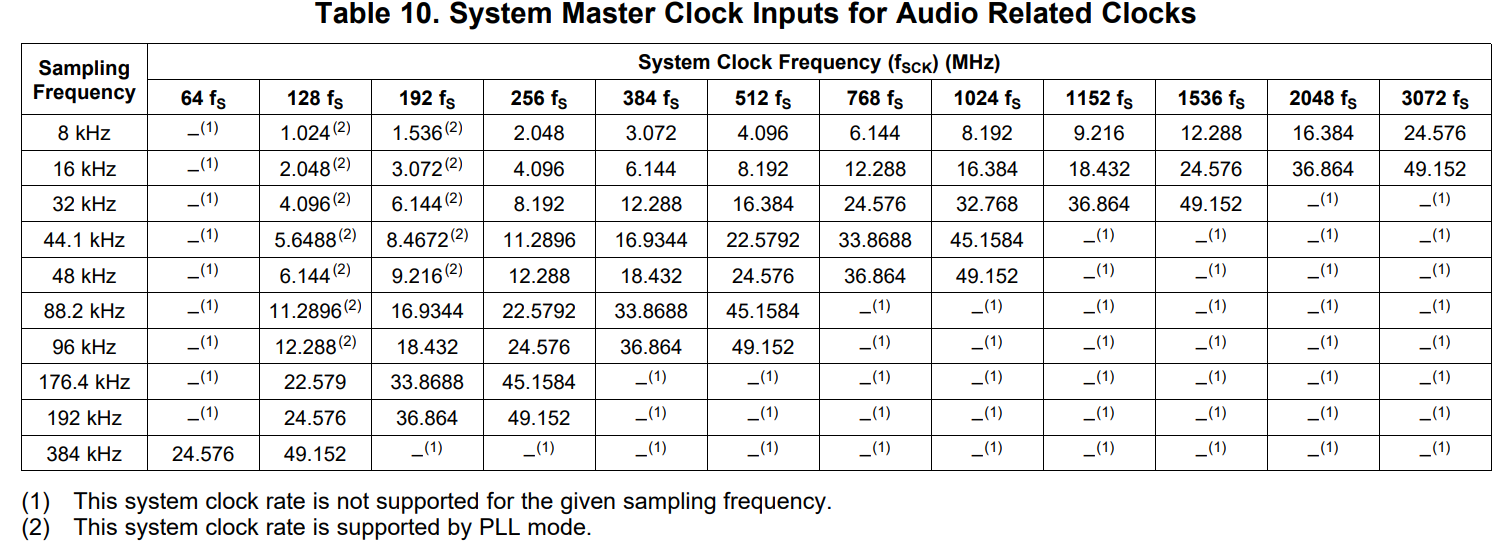

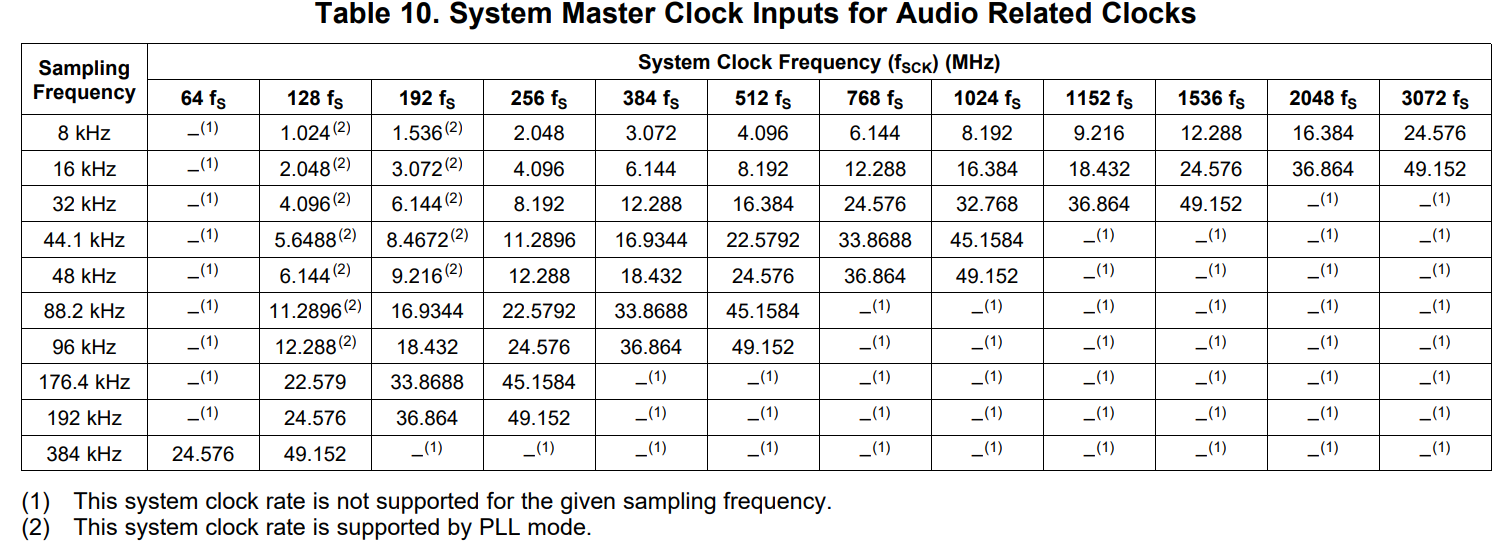

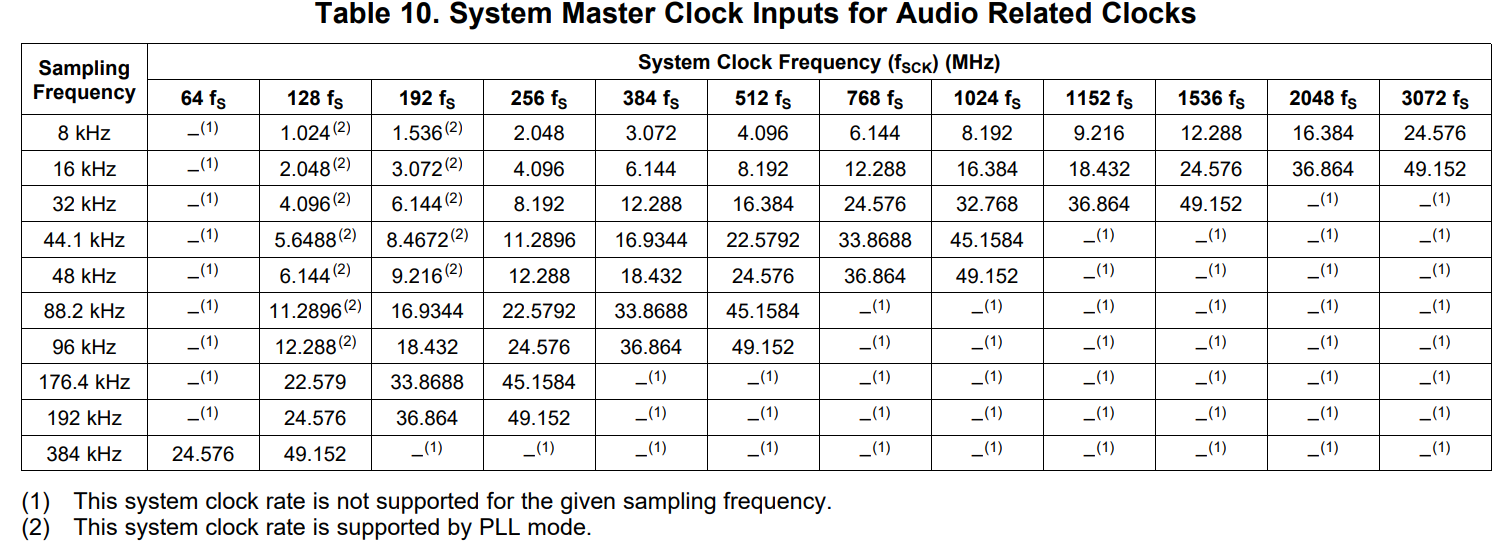

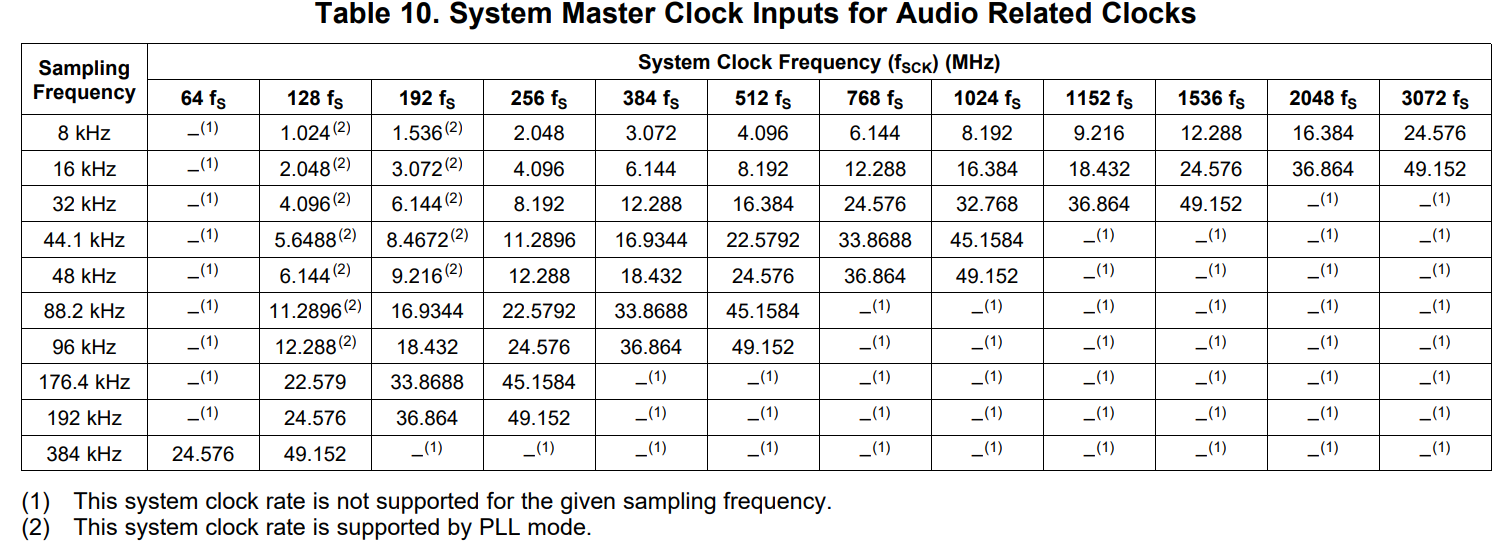

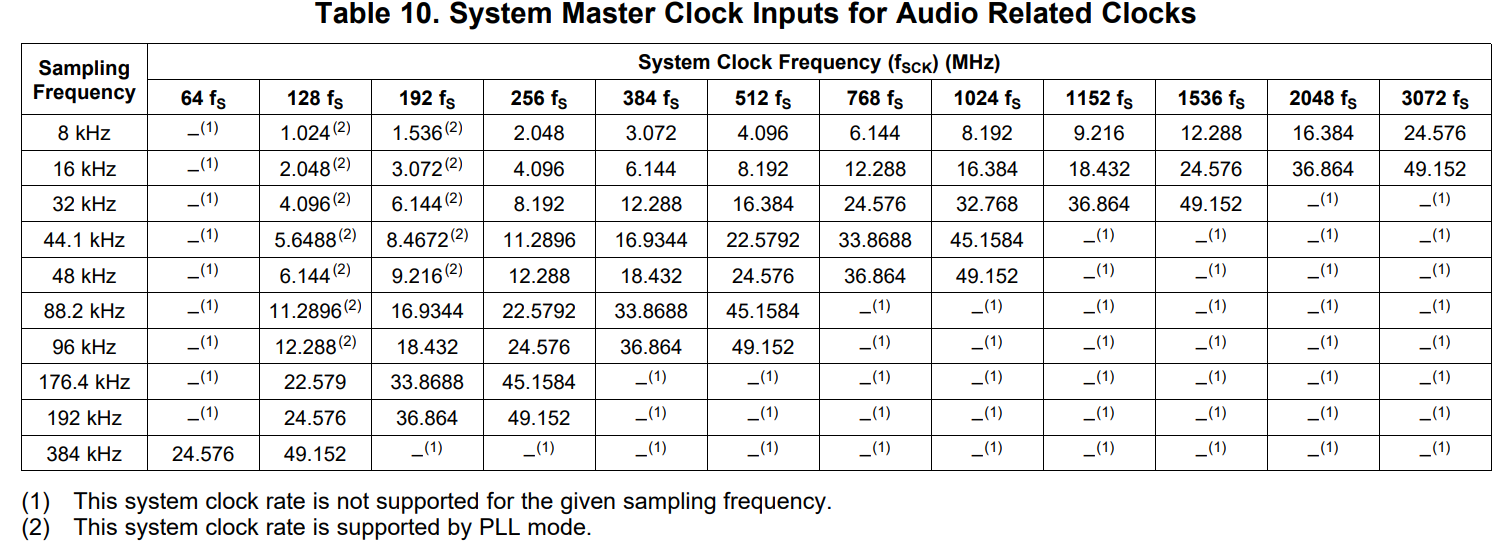

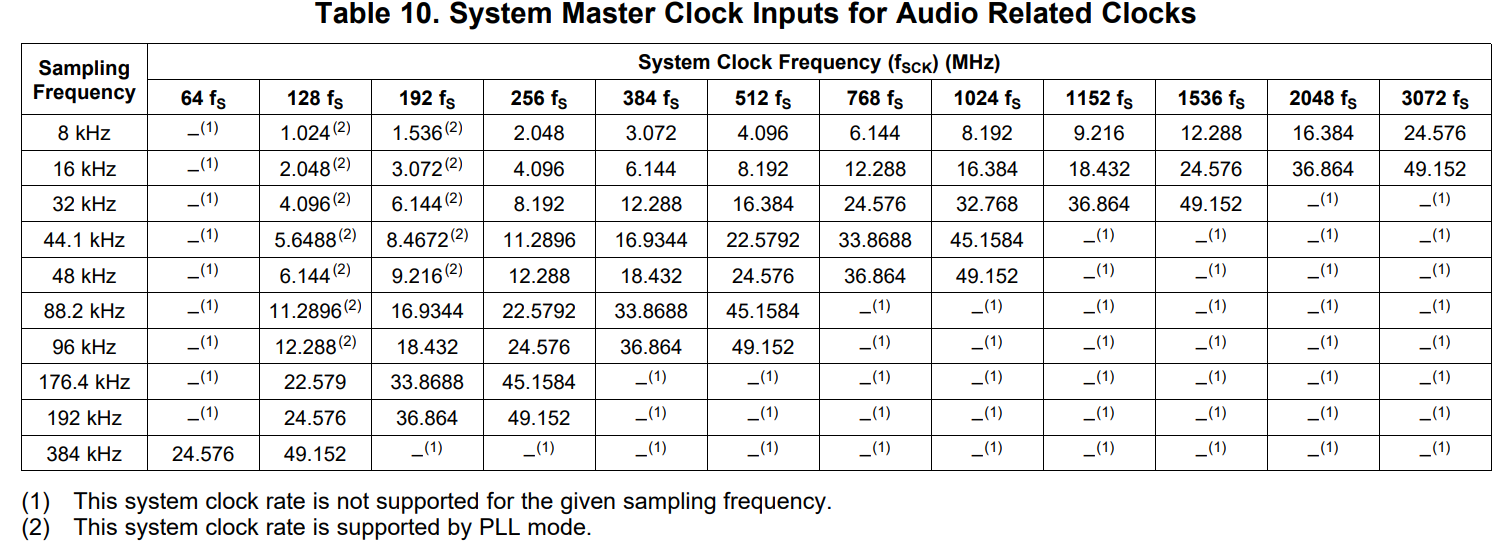

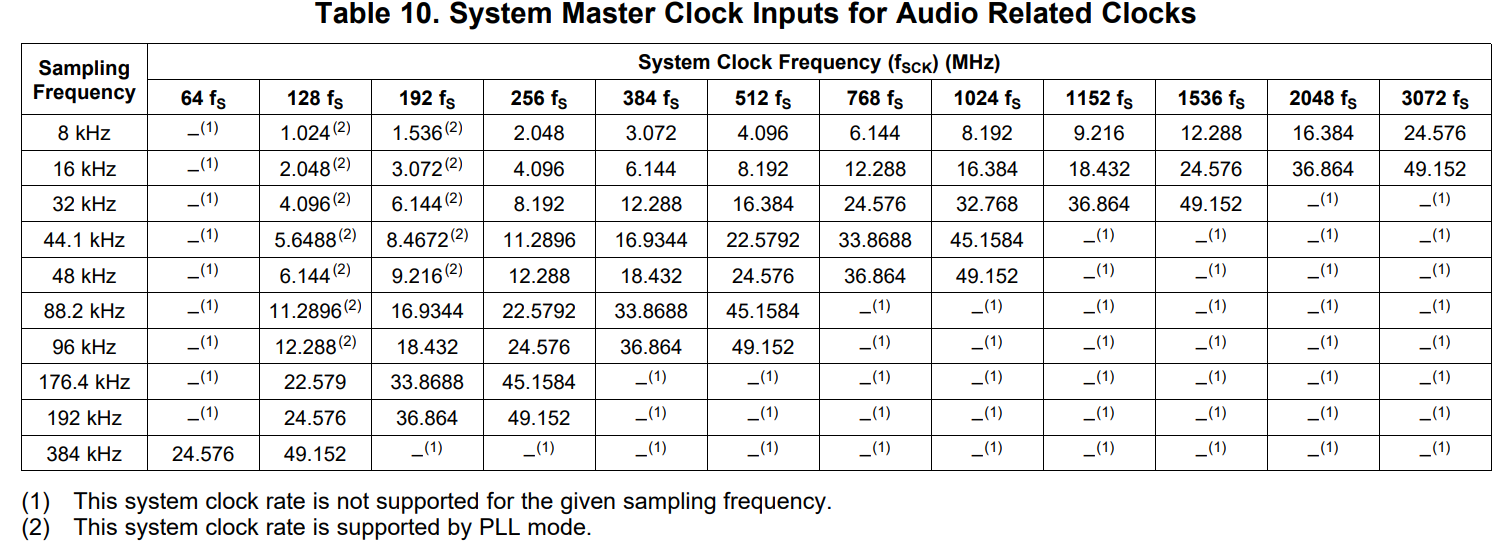

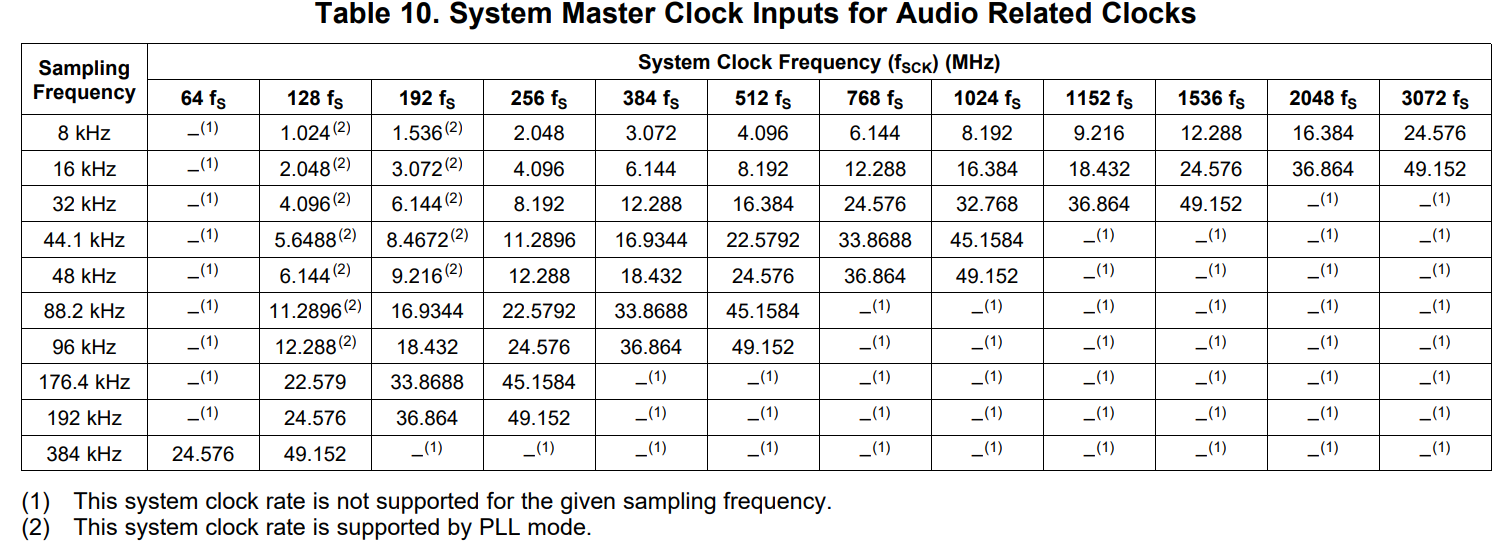

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

- In protocol I2S we have 3 signal + one none standard master clock(Mentioined by Olin Lathrop):

- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

- Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

- Question 4: Also the datasheet mentioned 1x/2x/4x/8x interpolatino is availible, but there isn't way to setting it, does it relate to MCK?How?

#4: Post edited

In protocol I2S we have 3 signal + one none standard master clock(Mentioined by Olin latrop):- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

- Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

- In protocol I2S we have 3 signal + one none standard master clock(Mentioined by Olin Lathrop):

- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

- Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

#3: Post edited

In protocol I2S we have 4 signal:- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

- Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

- In protocol I2S we have 3 signal + one none standard master clock(Mentioined by Olin latrop):

- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

- Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

#2: Post edited

- In protocol I2S we have 4 signal:

- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, gaind I couldn't find anything on datasheet.

- In protocol I2S we have 4 signal:

- 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock)

- Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work.

- Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):

-

- But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A).

- Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, again I couldn't find anything on datasheet.

#1: Initial revision

What is the role of master clock speed on DAC

In protocol I2S we have 4 signal: 1.data 2.lrck/fck (frame synchronizer) 3.bck (bit clock) 4.mck/sck (master clock) Question 1: Why we need master clock? I think simply some devices need clock to work, this master clock can provide clock for them to work. Question 2: In DAC IC PCM5102a we have specification about relation of master clock (sck) related to sampling frequency (lrck):  But what is the difference between these multiplier? In other word by providing higher or lower frequency clock for DAC what will change, what will happens? And how we can chose any of them? I can't find anything about it on it's [datasheet](https://www.ti.com/lit/ds/symlink/pcm5102a.pdf?ts=1680037818805&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FPCM5102A). Question 3: As you can see on the picture from datasheet appended above, whithout providing sck, it will uses it's own pll to generate clock for itself but according to picture we have two speed supported 128x and 192x. which one will be selected how, gaind I couldn't find anything on datasheet.