Post History

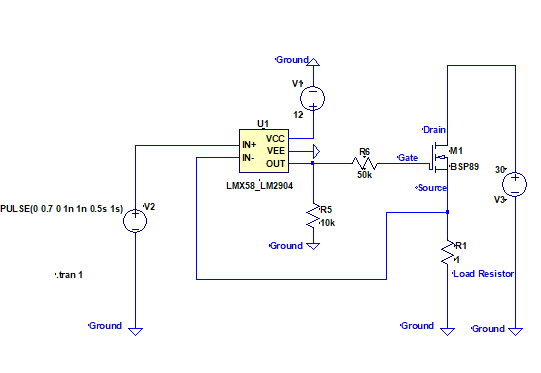

I benchtested below 0.7A constant current source circuit and observed few cycles of oscillation on drain current. With the help of bode plot analysis , I have managed to reduce the oscillations on ...

#1: Initial revision

MOSFET drain current ringing in saturation region

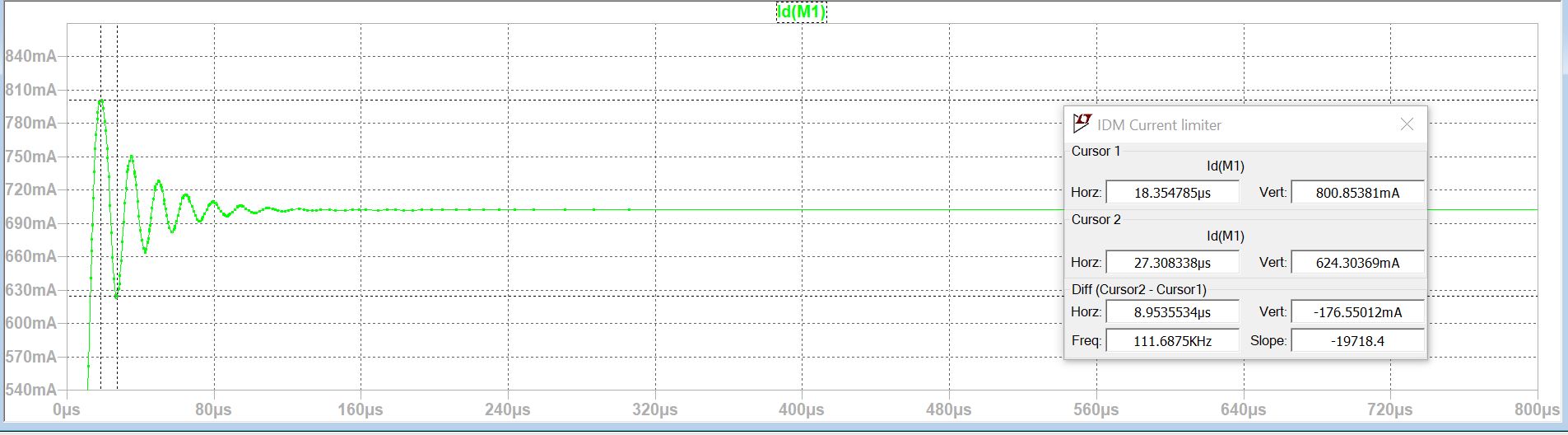

I benchtested below 0.7A constant current source circuit and observed few cycles of oscillation on drain current. With the help of bode plot analysis , I have managed to reduce the oscillations on drain current by increasing the phase margin to some acceptable level.  While doing the analysis , I observed in Ltspice and on the test bench that the amplitude of drain current oscillations and cycles increase as the drain voltage gets reduced from 30V to 7V.  ripple_drain_current_max@ 30V_Vd=78mA  ripple_drain_current_max@ 7V_Vd=176mA feedback element between drain terminal and gate terminal is miller capacitance. Is miller capacitance value getting reduced due to the application of higher voltage across it like it does in ceramic caps ( Vdg = 30V -Vg) and hence stores lesser charge compared to 7V ? and due to lesser stored charge , it gets dicharged in fewer cycles ? looking forward to the comments on this . Thanks